# PREEMPTABLE PARTIAL RECONFIGURATION FOR REAL-TIME COMPUTING WITH FPGAS

#### **INTRODUCTION**

Computer platforms are evolving towards heterogeneous architectures:

- FPGAs

- SoCs (FPGA + Hardware processor)

These new architectures and their features are attractive for real-time systems. The most attractive feature is:

• Dynamic Partial Reconfiguration (DPR)

#### **INTRODUCTION**

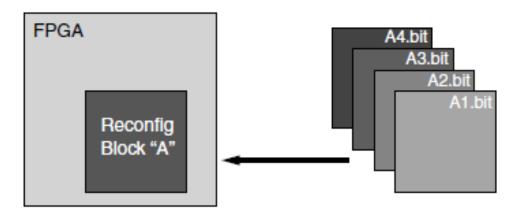

Dynamic partial reconfiguration enables the possibility to reconfigure a portion of the FPGA at runtime, while the rest of the FPGA continues to operate.

Different kind of systems can benefit from this feature to enhance the overall performance:

- Real-Time Systems

- Mixed-Criticality Systems

#### **INTRODUCTION**

The FPGA can be seen as a co-processor that exploits the hardware resources to carry out on-demand, computationally intensive tasks.

DPR allows the Core to load inside the FPGA the required hardware module only when it is necessary.

# **DPR PROBLEMS**

Currently, the main problem is the Reconfiguration Interface.

- Each reconfiguration process must be finished or aborted.

- No possibility to resume a reconfiguration process.

- There are more than one Reconfig. Interface but only one at a time can be used.

# **DPR PROBLEMS**

Currently, the main problem is the Reconfiguration Interface.

- Each reconfiguration process must be finished or aborted.

- No possibility to resume a reconfiguration process.

- There are more than one Reconfig. Interface but only one at a time can be used.

# The Reconfiguration Interface is NOT PREEMPTABLE!

# MULTI CORE MIXED CRITICALITY SYSTEMS

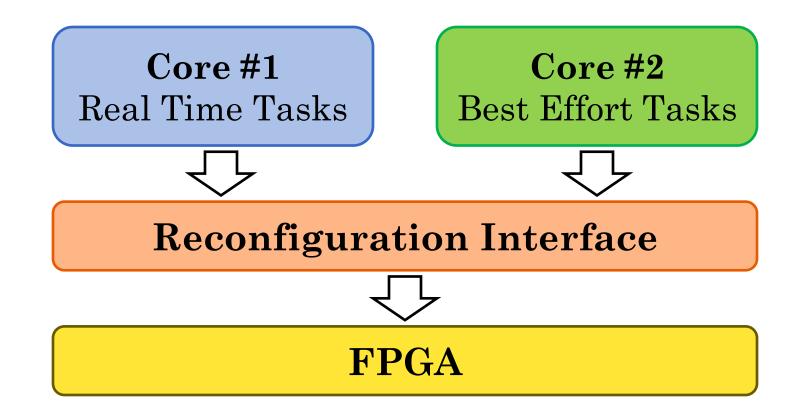

Both RT tasks and BE tasks can trigger a hardware reconfiguration. The reconfiguration interface will be a shared resource between the two cores and among all tasks.

- SW tasks with Fixed Priority scheduling

- Each SW task can issue a hardware reconfiguration process

- Reconfiguration process can not be preempted or aborted

- SW tasks with Fixed Priority scheduling

- Each SW task can issue a hardware reconfiguration process

- Reconfiguration process can not be preempted or aborted

- SW tasks with Fixed Priority scheduling

- Each SW task can issue a hardware reconfiguration process

- Reconfiguration process can not be preempted or aborted

- SW tasks with Fixed Priority scheduling

- Each SW task can issue a hardware reconfiguration process

- Reconfiguration process can not be preempted or aborted

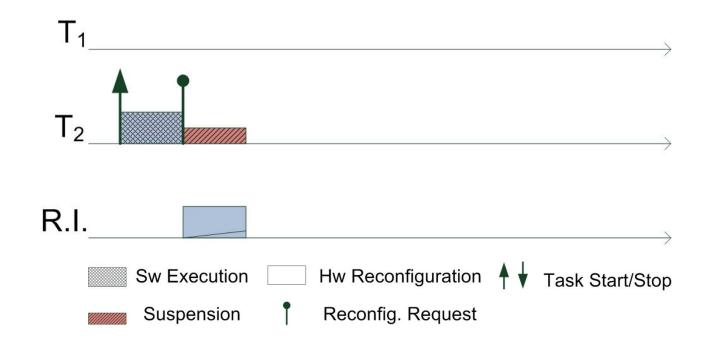

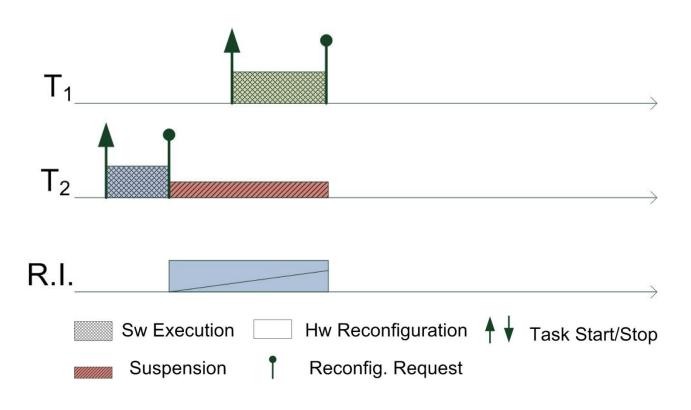

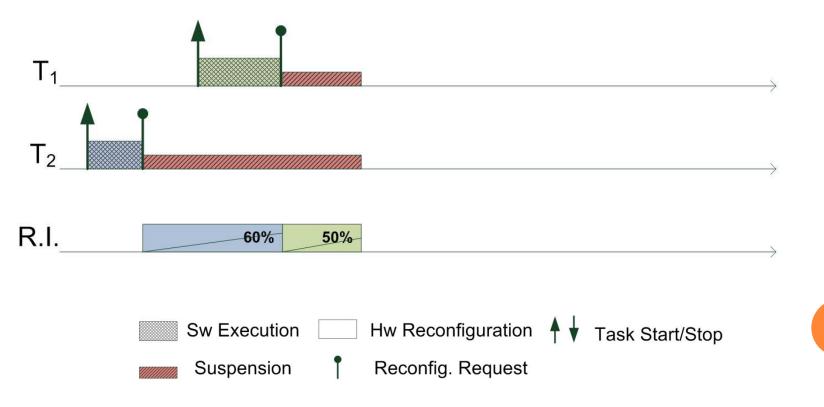

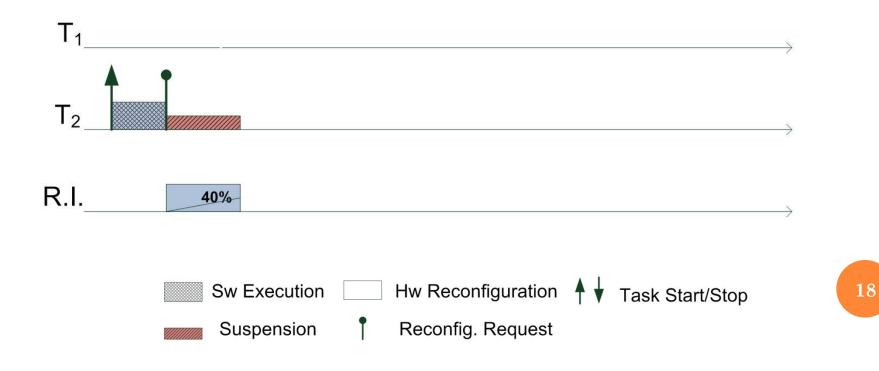

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration interface is not preemptive

- The reconfiguration process can be aborted

- The reconfiguration process must be resumed from scratch

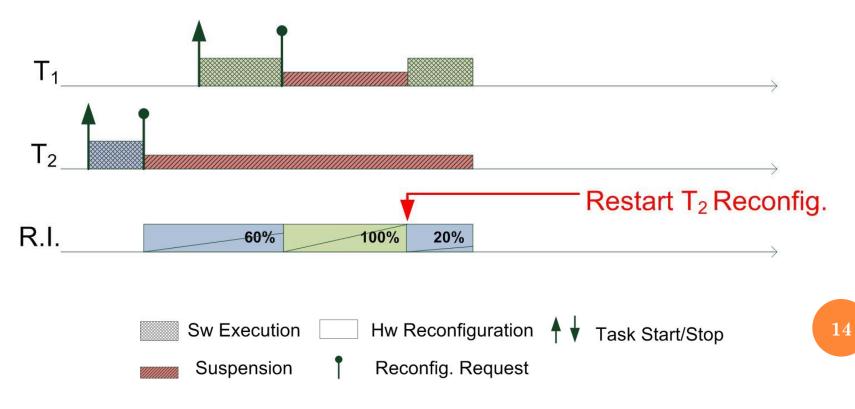

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration interface is not preemptive

- The reconfiguration process can be aborted

- The reconfiguration process must be resumed from scratch

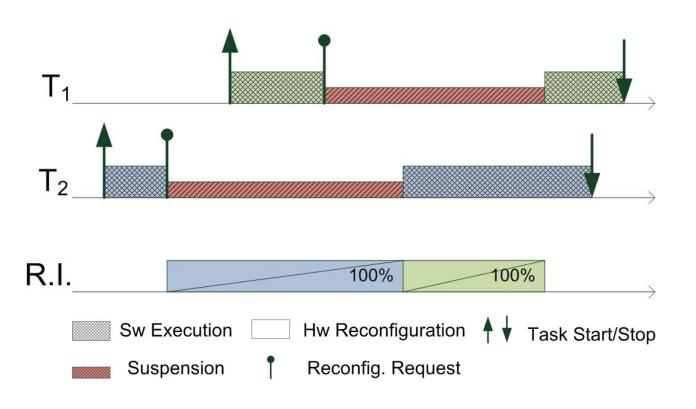

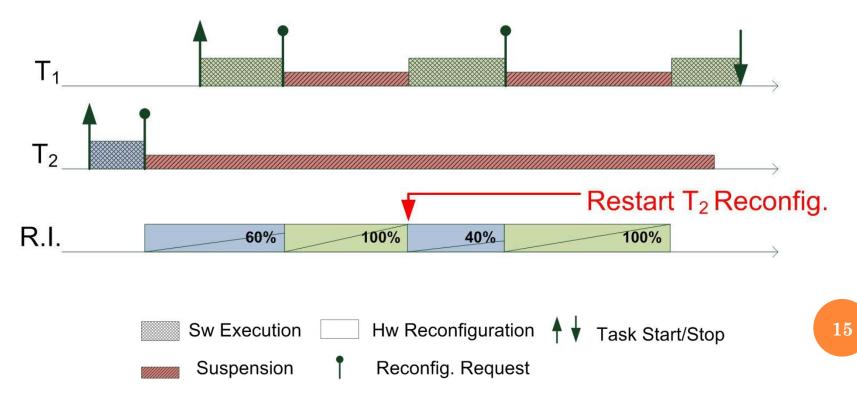

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration interface is not preemptive

- The reconfiguration process can be aborted

- The reconfiguration process must be resumed from scratch

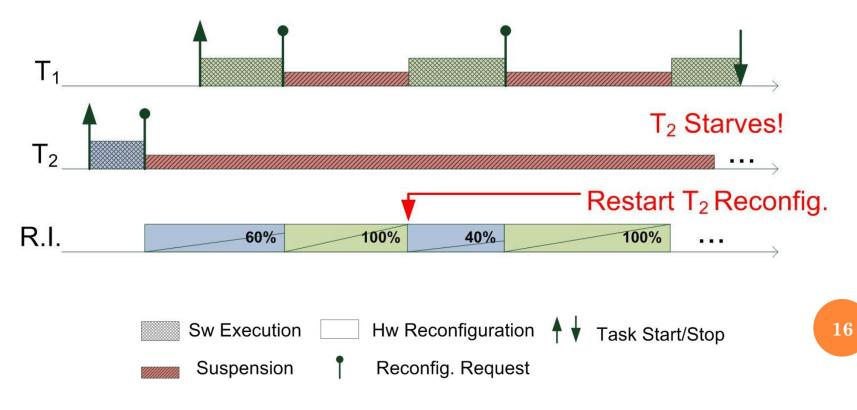

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration interface is not preemptive

- The reconfiguration process can be aborted

- The reconfiguration process must be resumed from scratch

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration interface is not preemptive

- The reconfiguration process can be aborted

- The reconfiguration process must be resumed from scratch

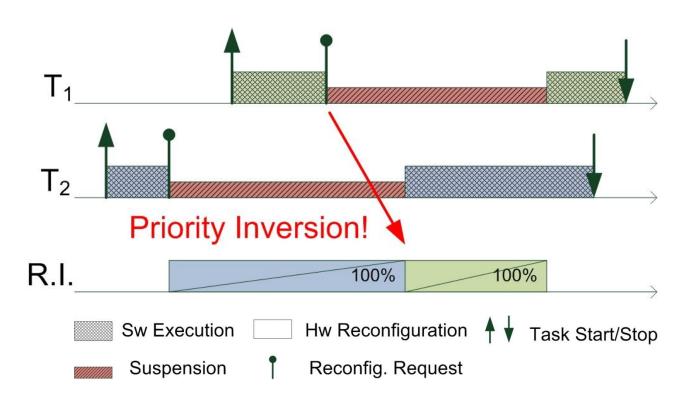

# **PRIORITY INVERTION AND STARVATION**

Without a preemptable interface:

- The delay experienced by the higher priority task could be very high.

- High priority tasks could miss their deadline!

- Upper bound of the delay experienced by the Best Effort task cannot be found.

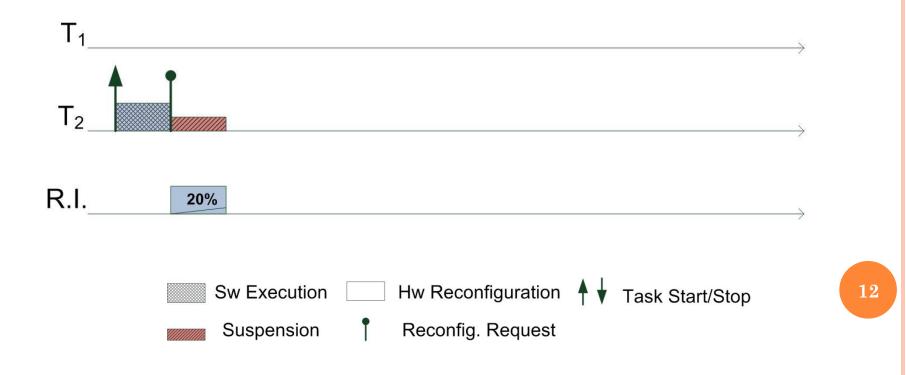

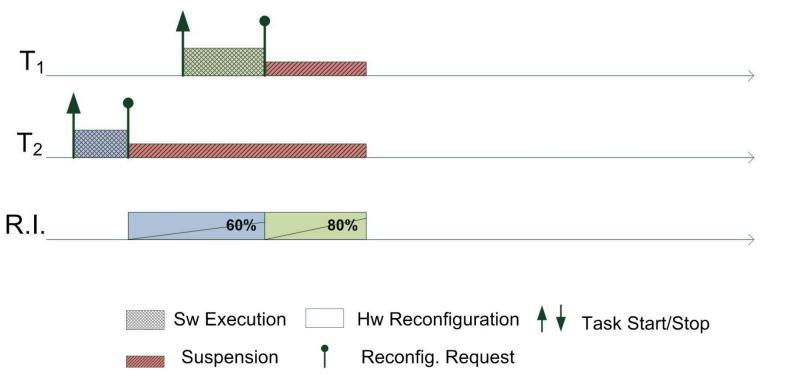

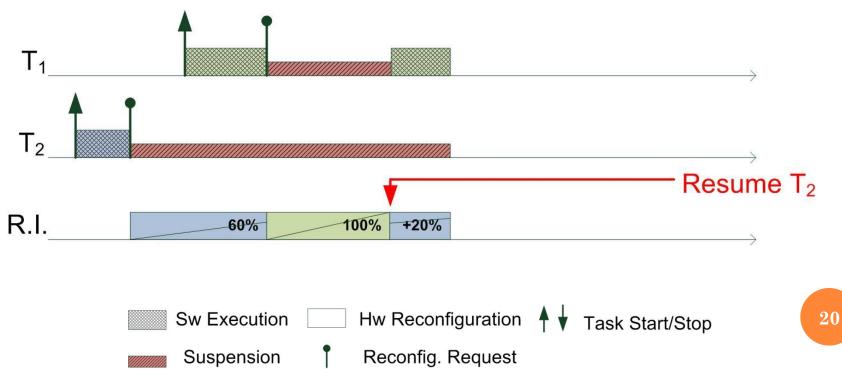

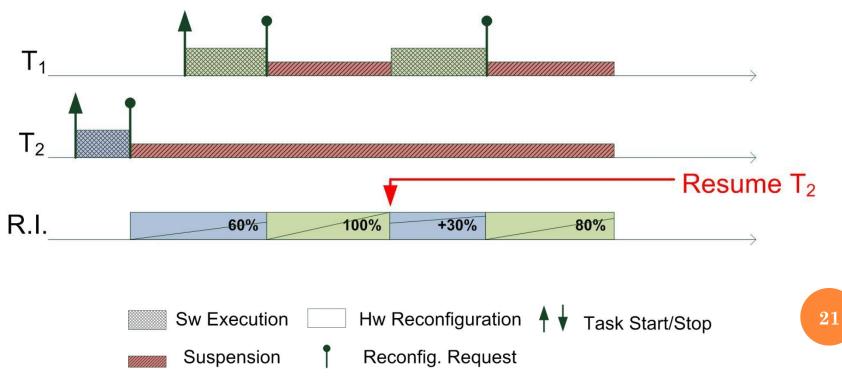

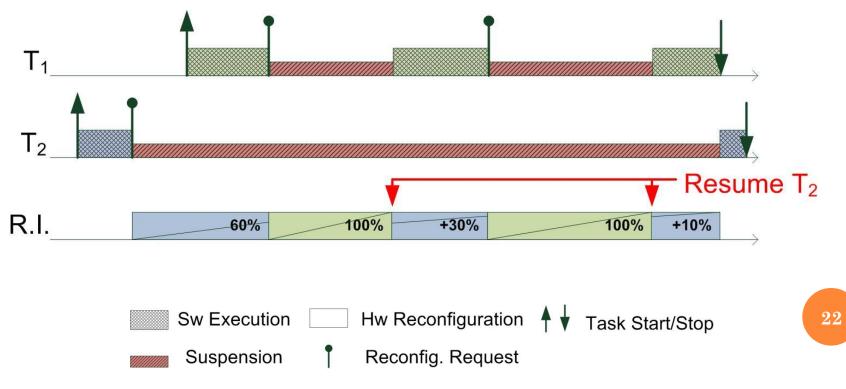

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration process is preemptable

- Hardware reconfiguration can be resumed

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration process is preemptable

- Hardware reconfiguration can be resumed

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration process is preemptable

- Hardware reconfiguration can be resumed

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration process is preemptable

- Hardware reconfiguration can be resumed

- Real Time task (T1) has priority over Best Effort task (T2)

- The reconfiguration process is preemptable

- Hardware reconfiguration can be resumed

#### BENEFITS

# With a preemptable interface:

- Performance of both Real Time and Best Effort tasks are improved.

- The delay experienced by the higher priority task can be reduced.

- The delay experienced by Best Effort tasks can be bounded.

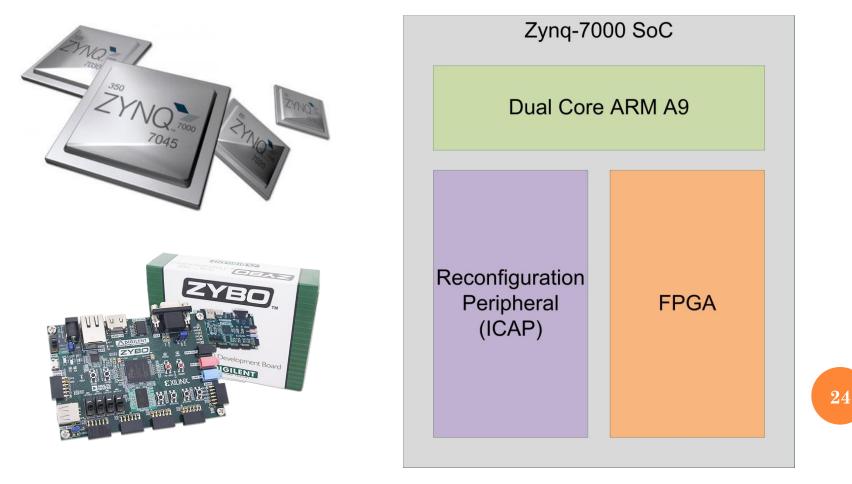

#### **IMPLEMENTATION**

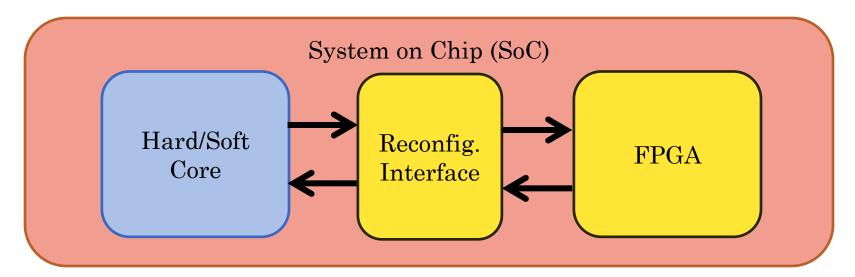

# Preemptable reconfiguration has been realized on a Xilinx Zynq-7000 platform.

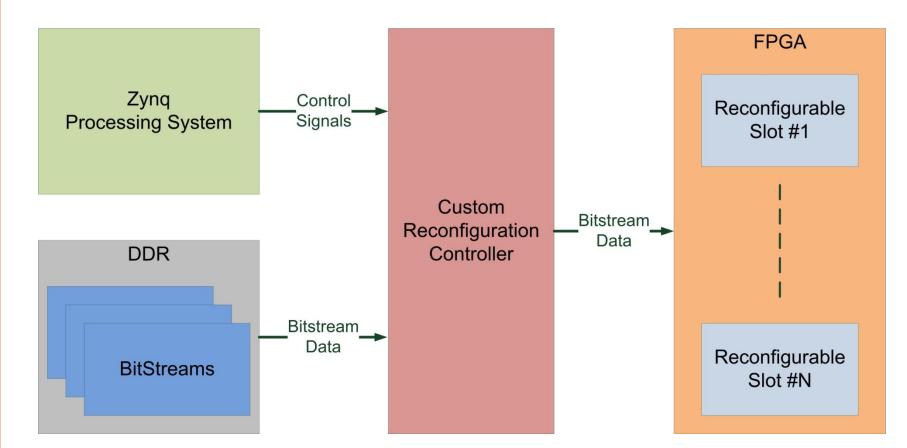

# **BASE SYSTEM OVERVIEW**

• Zynq Processing System can trigger a hardware reconfiguration by sending the bitstream to configure to the Reconfiguration Controller.

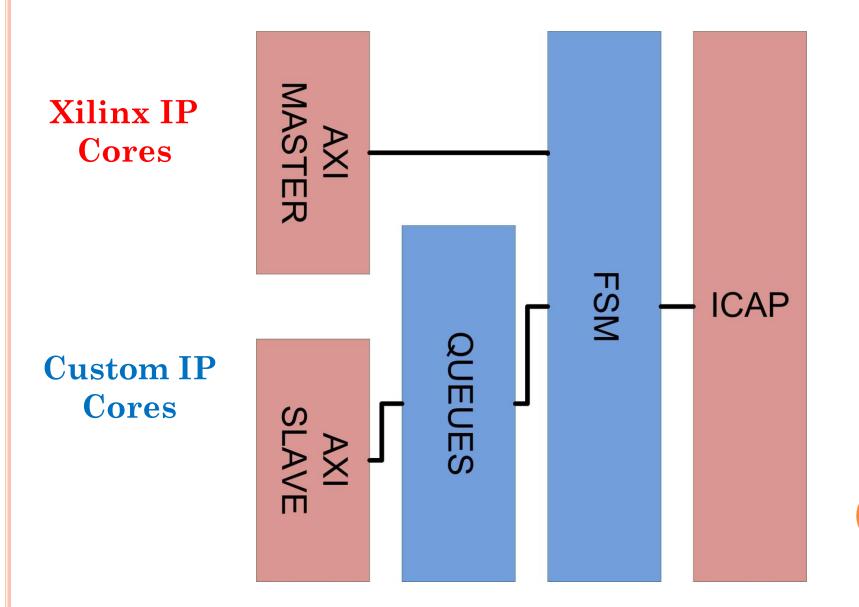

# **CUSTOM RECONFIGURATION CONTROLLER**

Xilinx IP Cores

AXI MASTER

**ICAP**

# **CUSTOM RECONFIGURATION CONTROLLER**

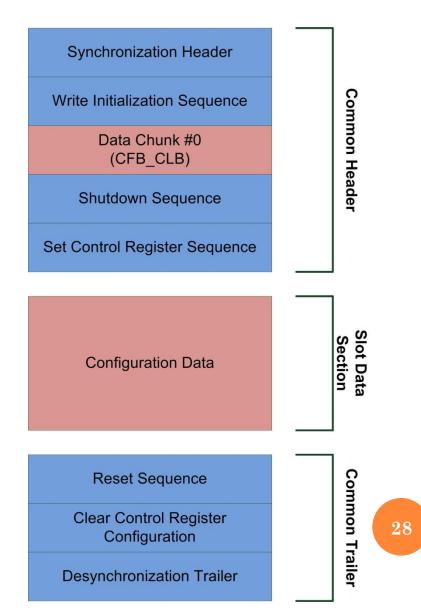

# VALID RESUMPTION POINTS

- Bitstream contain configuration data and commands.

- Commands control the Xilinx reconfiguration port (ICAP)

- The ABORT can be performed anywhere in the bitstream.

- Resumption point of reconfiguration must be carefully calculated.

# **CUSTOM RECONFIGURATION CONTROLLER**

| Software API     | High Level<br>Functions | PreemptReconfig();                                       |

|------------------|-------------------------|----------------------------------------------------------|

| Low-Level Driver | Software<br>Commands    | Abort();<br>SaveReconfigState();<br>StartNewReconfig();  |

| Hardware         | Hardware<br>Commands    | 0x09000000;<br>0x07000000;<br>0x0B000000;<br>0x02000000; |

# **CUSTOM RECONFIGURATION CONTROLLER**

| Software API     | High Level<br>Functions | PreemptReconfig();                                       |

|------------------|-------------------------|----------------------------------------------------------|

| Low-Level Driver | Software<br>Commands    | Abort();<br>SaveReconfigState();<br>StartNewReconfig();  |

| Hardware         | Hardware<br>Commands    | 0x09000000;<br>0x07000000;<br>0x0B000000;<br>0x02000000; |

• The hardware layer guarantees worst-case latency bounds on the commands it processes, even on the reconfiguration itself when a memory bandwidth is guaranteed.

#### **PROJECT FLOW**

Hardware Design with Partial Reconfiguration

Output: One Bitstream of each Accelerator for each Reconfigurable Slot.

### **PROJECT FLOW**

Hardware Design with Partial Reconfiguration

Output: One Bitstream of each Accelerator for each Reconfigurable Slot.

Generate Header File from Bitstream Output: Header file with all Resumption Points of each Bitstream.

### **PROJECT FLOW**

Hardware Design with Partial Reconfiguration

Output: One Bitstream of each Accelerator for each Reconfigurable Slot.

Generate Header File from Bitstream Output: Header file with all Resumption Points of each Bitstream.

Software Design with Reconfig. APIs

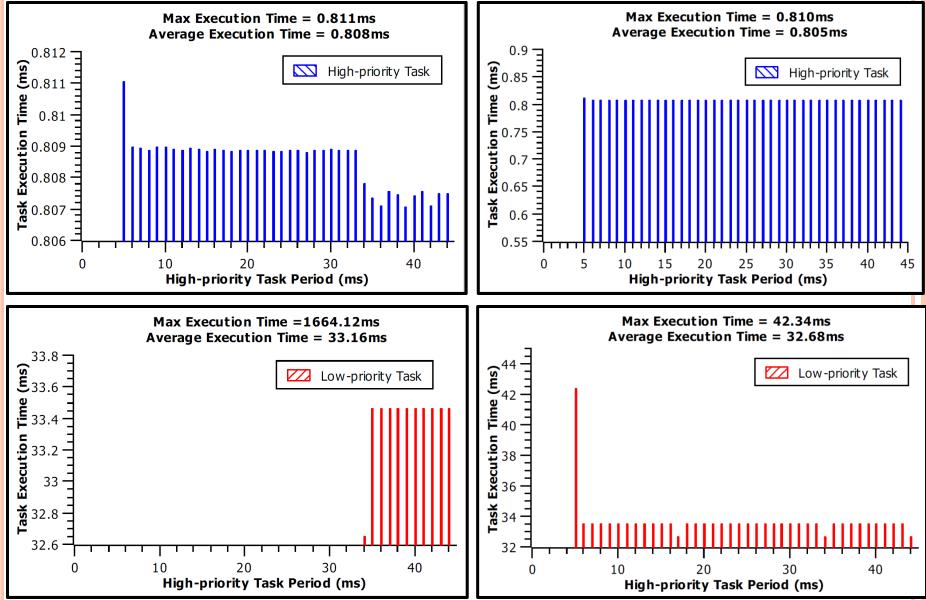

#### MEASURED RESULTS

• High priority task

- Period: from 5ms to 44ms (1ms step)

- Reconfig. time: 0.79ms

- Low priority task

- Period: 50ms

- Reconfig. time: 32.63ms

|            | Low Priority Task                           |                                             | High Priority Task                          |                                             |

|------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|

|            | Max.<br><mark>Observed</mark><br>Exec. Time | Avg.<br><mark>Observed</mark><br>Exec. Time | Max.<br><mark>Observed</mark><br>Exec. Time | Avg.<br><mark>Observed</mark><br>Exec. Time |

| No Abort   | 33.46 ms                                    | 32.68 ms                                    | $2.45~\mathrm{ms}$                          | $0.805 \mathrm{\ ms}$                       |

| Abort      | 1664.12 ms                                  | 33.16 ms                                    | 0.811 ms                                    | 0.808 ms                                    |

| Preemption | 42.34  ms                                   | 32.68 ms                                    | 0.810 ms                                    | $0.805 \mathrm{\ ms}$                       |

#### MEASURED RESULTS

• High priority task

- Period: from 5ms to 44ms (1ms step)

- Reconfig. time: 0.79ms

- Low priority task

- Period: 50ms

- Reconfig. time: 32.63ms

|            | Low Priority Task              |                                | High Priority Task             |                                |

|------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

|            | Max.<br>Observed<br>Exec. Time | Avg.<br>Observed<br>Exec. Time | Max.<br>Observed<br>Exec. Time | Avg.<br>Observed<br>Exec. Time |

| No Abort   | 33.46 ms                       | 32.68 ms                       | $2.45~\mathrm{ms}$             | 0.805 ms                       |

| Abort      | 1664.12 ms                     | 33.16 ms                       | 0.811 ms                       | 0.808 ms                       |

| Preemption | 42.34  ms                      | 32.68 ms                       | 0.810 ms                       | $0.805 \mathrm{\ ms}$          |

#### MEASURED RESULTS

#### Starvation Experiment

#### **Preemption Experiment**

# CONCLUSIONS

- Design and realization of Preemptable Reconfiguration with guaranteed latencies

- Custom Reconfiguration Controller

- Software driver, API

- Tools to analyze and manipulate bitstreams

- Base application developed on a RealTime OS (FreeRTOS) that benefits from having Preemptable Reconfiguration