## Dynamic Trade-Off Management for CPS

Francesca Palumbo, Claudio Rubattu, Carlo Sau, Tiziana Fanni, Paolo Meloni, Luigi Raffo

Abstract—Functional approximate computing methodologies combined with coarse-grained reconfigurable design approaches are prospectively suitable to address variable run-time trade-off management typical of evolvable and adaptive cyber-physical systems. This abstract presents preliminary achievements in HEVC interpolation filters acceleration to be used to trade quality for energy in an ocean monitoring use case to be developed in an H2020 project.

## I. CONTEXT AND CONTRIBUTION

N the era of Cyber-Physical Systems (CPS), designers need to cope with complex devices composed of different interacting and deeply intertwined components, with multiple and distinct behavioural modalities variable over time, that contribute concurrently to determine the behaviour of the system as a whole. The European Project Cross-layer modEl-based fRamework for multi-oBjective dEsign of Reconfigurable systems in unceRtain hybRid envirOnments (CERBERO) aims at developing a continuous design environment for CPS, including modelling, deployment and verification [1]. CPS are highly evolvable and adaptive systems where functional (F) and non-functional (NF) requirements are constantly subjected to variation. The efficient support of runtime reconfiguration, taking into account requirements adjustments, is among the CERBERO expected outcomes.

At the physical level, application specific heterogeneous accelerators based on the Coarse Grained Reconfigurable (CGR) approach can suite the scope of providing flexibility and dynamic adaptation to changeable F/NF requirements. Indeed CGR platforms already demonstrated to be effective in flexible, but constrained, scenarios [2]. We believe that they can naturally tackle the adaptation needs in CPS designs, by guaranteeing dynamic trade-off management among relevant system metrics. Nevertheless, dealing with CGR platforms is not so straightforward, requiring a deep knowledge on the functionalities/kernels to be implemented. To mitigate this issue automated or semi-automated design environments have been proposed in literature [3], [4]. Our studies aims at demonstrating, within the CERBERO project, that automated flows may not affect trade-off guarantees.

## II. PRELIMINARY ACHIEVEMENTS AND CURRENT ACTIVITIES

High Efficiency Video Coding (HEVC) is the most recent video compression standard [5], which provides improved

Authors would like to thank the EU commission for funding the CERBERO project (#732105).

video quality for a given bit rate with respect to its predecessors, but it is still power hungry. In HEVC decoding, motion compensation represents the most computationally intensive task. To compensate motion vectors with fractional values, a block is predicted by interpolating its reference block. Interpolations are implemented with a couple of N taps 1-D FIR filters, for horizontal and vertical directions. Different solutions for energy saving in HEVC interpolation filters have been conceived. To reduce and dynamically tune the energy consumption of the interpolator, Nogues et al. [6] exploited functional approximate computing. They demonstrated in software that it is possible to waive quality (# of taps reduction) for energy. In hardware, [7] presents an analogue approach leveraging on CGR architectures: starting from a legacy implementation of the interpolation filters, run-time adaptive solutions can be derived by dynamically excluding some taps from the computation.

Fig. 1. CGR HEVC filters.

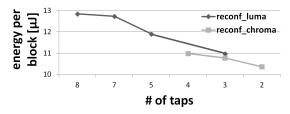

Figure 1 presents a flavor of the achievable results. Adaptive approximate filters for luma (reconf\_luma) and chroma (reconf\_chroma) can be derived from the legacy one by excluding stages from the computation. Consumption in excluded stages is limited by means of power saving techniques, such as clock gating and operand isolation. These CGR filters effectively trade quality for energy.

In CERBERO, we intend to extend these studies to tackle CPS designs and estimate trade-offs at model level. This will enable embedding runtime models in the hw/sw reconfiguration manager to address changeable requirements variations.

## REFERENCES

- [1] M. Masin, et al. Cross-layer design of reconfigurable cyber-physical systems, DATE 2017.

- [2] M. Yan, et al. Prodfa: Accelerating domain applications with a coarsegrained runtime reconfigurable architecture, ICPADS 2012.

- [3] G. Ansaloni, et al. Integrated kernel partitioning and scheduling for coarse-grained reconfigurable arrays, TCAD 2012.

- [4] C. Sau, et al. Automated design flow for multi-functional dataflow-based platforms, JSPS 2016.

- [5] G.J. Sullivan, et al. Overview of the high efficiency video coding (HEVC) standard. TCSVT 2012.

- [6] E. Nogues, et al. A modified HEVC decoder for low power decoding, CF 2015.

- [7] C. Sau, et al. Challenging the Best HEVC Fractional Pixel FPGA Interpolators with Reconfigurable and Multi-frequency Approximate Computing, IEEE ESL, 2017, vol.PP, no.99, pp.1-1. doi: 10.1109/LES.2017.2703585.

F. Palumbo and C. Rubattu are with the University of Sassari (Italy), E-mail:(fpalumbo,crubattu)@uniss.it

C. Sau, T. Fanni, P. Meloni and L. Raffo are with University of Cagliari (Italy), (name.surname)@diee.unica.it